英特尔雄心勃勃的 18A 节点在临近量产时正面临两个重大障碍:良品率徘徊在 10% 以下,SRAM 密度与台积电的竞争产品 N2 工艺相比处于劣势。 这些挑战可能会阻碍该节点在英特尔下一代 CPU、人工智能和定制芯片组合中的部署。

最近有报道指出,在 18A 节点上正面临着巨大的良率挑战,可能会推迟其量产时间。 据韩国《朝鲜日报》报道,目前的良品率低于 10%,这意味着每生产 10 个芯片就有近 9 个存在缺陷。

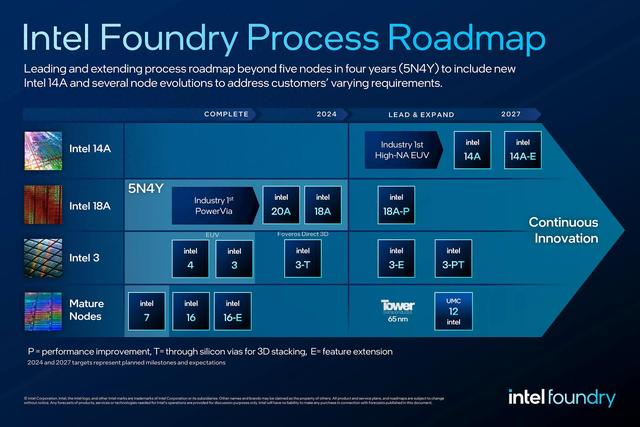

这是一个重大问题,尤其是英特尔已经取消了面向代工厂客户的 20A(2 纳米级)工艺节点,并将资源转移到 18A(1.8 纳米级)节点。 如果低于 10% 的良品率被证明是准确的,那么该节点很显然将不适合商业生产,至少在做出重大改进之前是如此。

在这些尖端节点上将晶体管封装到越来越密集的布局中是一个巨大的工程障碍,影响着整个半导体行业。 3 纳米以下工艺的代工良率目前低于 50%,其 Gate-All-Around (GAA) 技术的良率据称低至 10%至 20%。

不过,我们有理由对英特尔的 18A 节点持乐观态度,因为该公司在预计 2025 年量产之前,仍有几个月的时间来完善该工艺。 18A 节点将为英特尔服务器芯片、移动 CPU 和定制人工智能芯片等备受瞩目的产品提供动力,im钱包官网下载其潜在回报是巨大的。

如果英特尔能在未来几个月内将 18A 的良品率迅速提高到可观的水平(超过 60%),那么该节点仍有可能推动公司下一代产品的发展。

尽管如此,良率问题并不是英特尔在 18A 方面面临的唯一挑战。 据报道,台积电在另一个关键领域也取得了优势: SRAM 密度。

根据 ISSCC 2025 推进计划,台积电的 N2(2nm 级)节点将高密度 SRAM 位单元缩小到约 0.0175 μm²,密度达到 38Mb/mm²。 相比之下,Intel 的 18A 节点实现了 0.021 μm² 和 31.8Mb/mm²,更接近于台积电的上一代 N3E 和 N5 节点,这是一个明显的差异。

随着芯片设计需要更多的 SRAM,提高这些微小存储单元的密度对于保持紧凑、高效的设计至关重要。 这就是全栅极(GAA)晶体管发挥作用的地方。

与传统的鳍式场效应晶体管(finFET)相比,GAA 晶体管通过控制各面的沟道,实现了更严格的扩展。 这种严格的控制减少了小尺寸下的漏电现象,从而实现了更高密度的 SRAM。 英特尔和台积电都在使用 GAA 来缩小其 SRAM 位元,但台积电通过其 N2 节点成功地将它们封装得更加密集。